Shenzhen Filetti Technology Co., Ltd. was established in 2022.

Strategically headquartered in Shenzhen – China’s world-renowned

electronics hub ("China Electronics First Street") – Filetti

Technology is a professional distributor of electronic components.

We leverage our prime location in the heart of Asia’s supply chain

ecosystem to deliver efficient, reliable end-to-end sourcing

solutions to customers worldwide.

Core Strengths:

- Global Supply Chain Access: Direct sourcing channels with leading

manufacturers across Asia-Pacific.

- Demand Fulfillment Expertise: Agile inventory management for urgent

& volume orders.

- Quality Assurance: Rigorous component verification and traceability

protocols.

- Technical Support: Dedicated engineering assistance for BOM

optimization and lifecycle management.

Why Partner With Us?

As your extension in Shenzhen, we bridge global innovation with

seamless component supply – reducing risks, accelerating

time-to-market, and ensuring supply chain resilience for OEMs, EMS

providers, and R&D teams.

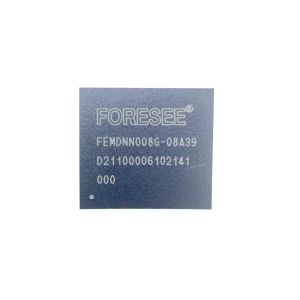

The company mainly deals in imported brands such as ON

Semiconductor, INFINEON, ST, VISHAY, AVAGO, TOSHIBA, DIODES, FUJI,

MaxLinear, NEXPERIA, GOWIN, etc. Our product line covers brands

such as BL Beileng, 3PEAK, SILAN, NOVOSENSE, UTC U-Times, MACMIC,

STARPOWER, SILLUMIN and TM Tianwei, and is available in Europe, the

United States, Japan, Taiwan of China, China and other regions. Our

business categories include: IGBT modules, IGBT single tubes,

MOSFETs and other power devices, as well as optocouplers, various

IC chips, diodes and transistors and other supporting products. The

company has established a one-stop business model covering sales

and procurement throughout Asia. The company has always adhered to

the business philosophy of "mutual benefit and mutual trust".

"Win-win cooperation". Adhering to the development principle of

"keeping promises, emphasizing cooperation and planning for the

long term", a complete quality management system has been

established. With high-quality products, reasonable prices,

immediate supply and professional supporting services, it has won

wide recognition in the industry and trust from customers. Stable

and long-term cooperation!